The 74xx595 devices contain an 8-bit, serial-in parallel-out (SIPO). The storage register has parallel 3-state outputs. Separate clocks are provided for both the shift and storage register. The shift register has a direct overriding clear (SRCLR) input, serial (SER) input and serial outputs for cascading. When the output-enable (OE) input is high, the output are in high impedance state.

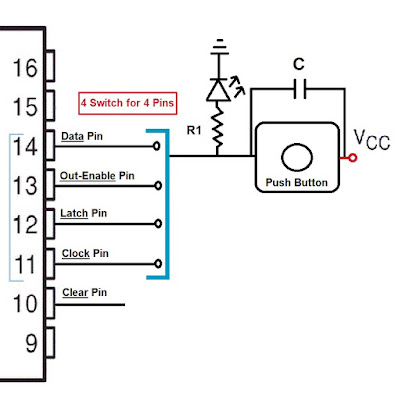

This Switch Diagram Configuration is for Data, Out-Enable, Latch, Clock Pins as shown above in picture

This is whole working circuit for shift register but there is a slight change in the Clear Pin, in this push button is grounded

Pin Configuration

Circuit Diagram

- Vcc - 5Volts

- R1 - 1k ohms

- C - 47microfard

- R2 - 1k ohms

- R3 - 10k ohms